TMS320x280x ADC模块是一个12位流水线模数转换器,该转换器的模拟电路,在本文称为核心,包括前端模拟多路复用器(MUXs)、采样保持(S/H)电路、转换核心、稳压器和其他模拟支持电路。数字电路在本文称为封装器,包括可编程转换序列器、结果寄存器、模拟电路接口、设备外围总线接口以及其它片上模块的接口。

Note:适用于TMS320x280x,TMS320x2801x,TMS320x2804x DSP

Note:定序器、排序器、测序器在本文指的是同一模块

1 介绍

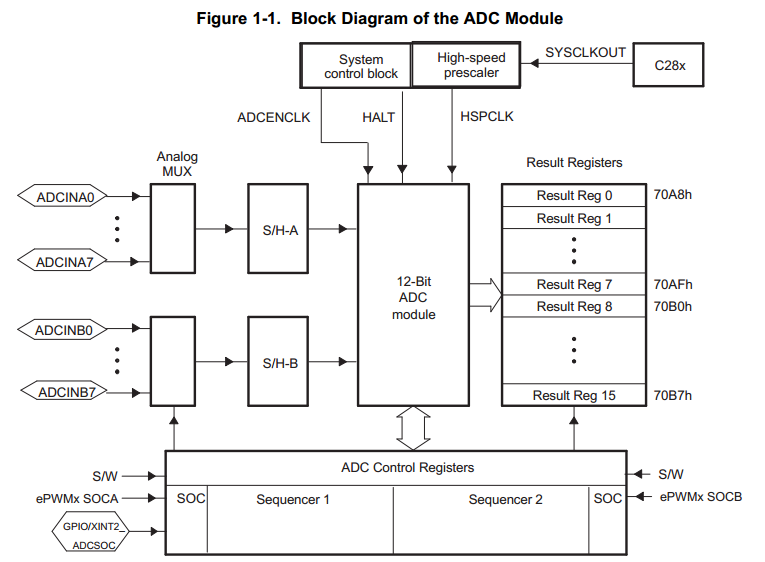

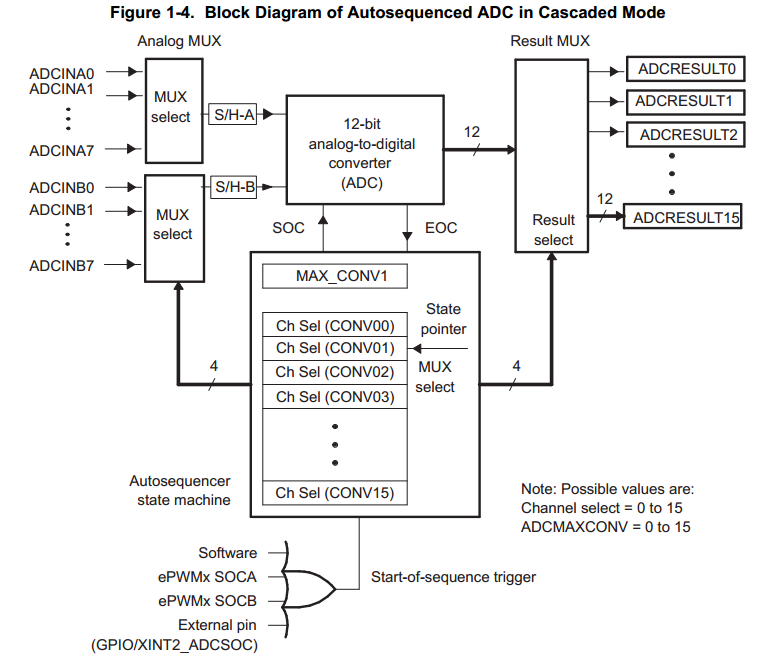

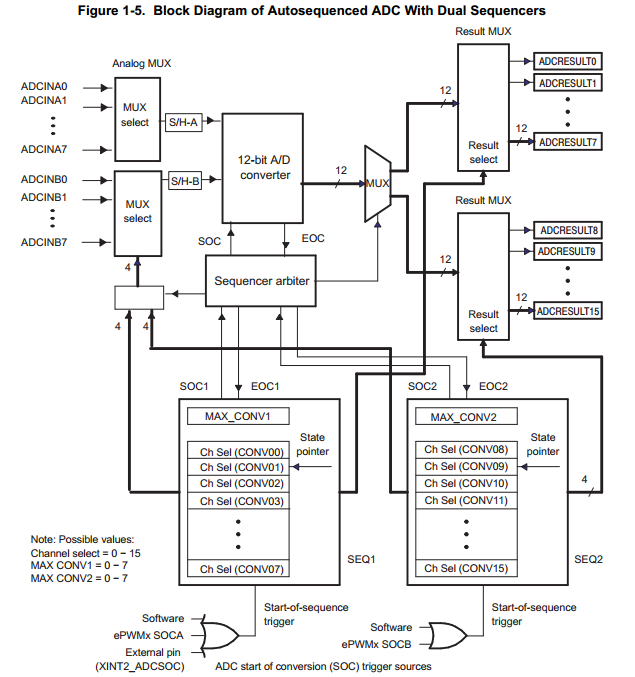

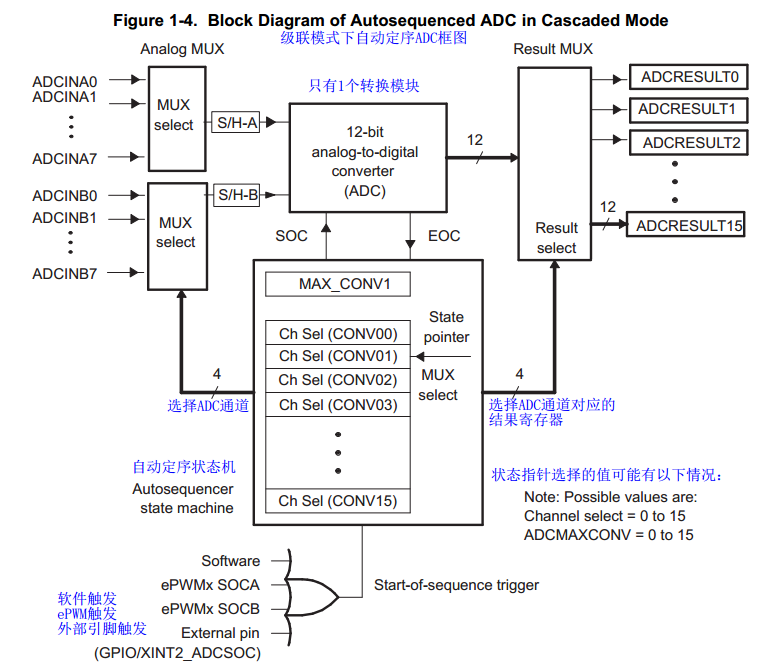

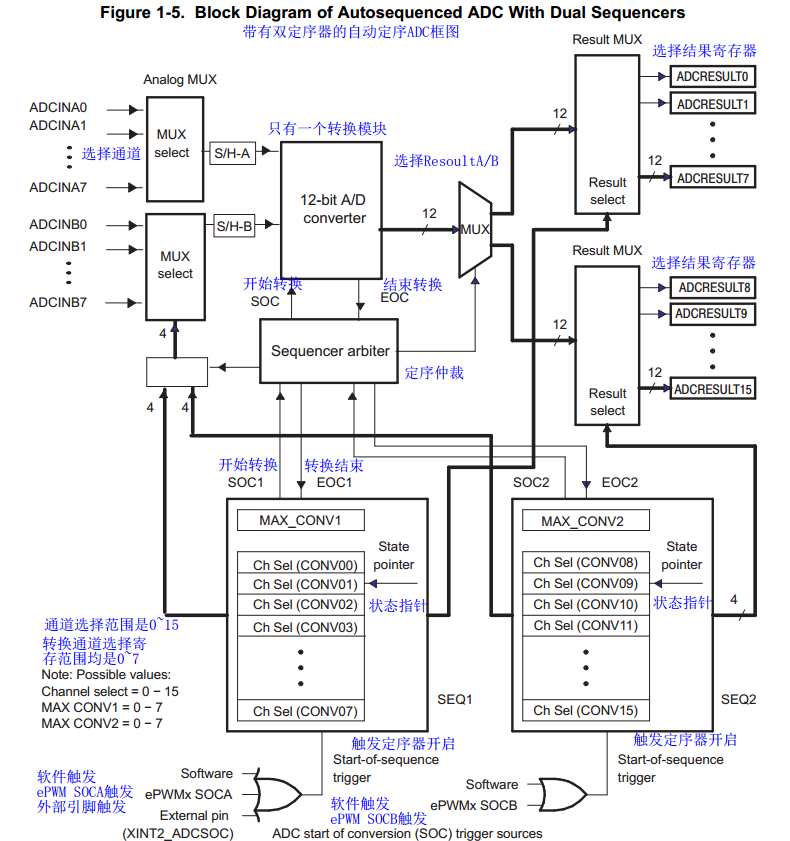

ADC模块有16个通道,可以配置为两个独立的8通道模块,用于ePWM模块。两个独立的8通道模块可以级联成一个16通道模块。虽然有多个输入通道和两个序列器,但是ADC模块只有一个转换器。ADC模块框图如下所示:

两个8通道模块可以自动排序进行转换,每个模块都可以选择通过模拟MUX提供的8个通道中的任何一个。在级联模式下,自动排序器的功能为单个16通道定序器。在每个序列器上,一旦转换完成,所选择的通道值存储在其各自的ADC结果寄存器中。自动测序允许系统多次转换相同的通道,允许用户执行过采样算法。这种过采样比传统的单采样转换结果提供了更高的分辨率。

ADC模块的功能包括:

内置双采样保持(S/H)的12位ADC核心;

支持同时采样和顺序采样模式;

支持模拟输入电压:0V~3V;

快速转换时间运行在12.5MHz、ADC时钟或6.25Msamples;

支持16通道,多通道输入;

自动测序功能单个会话中提供多达16个“自动转换”,每个转换可以编程为选择16个输入通道中的任何一个;

测序器可以作为两个独立的8状态测序器或作为一个大的16状态测序器(即两个级联的8状态测序器);

16个结果寄存器(可单独寻址)用于存储转换值。

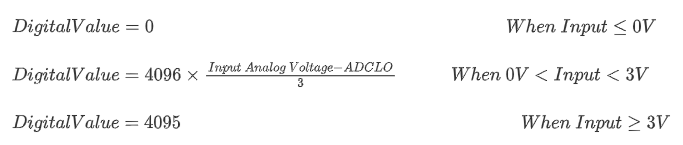

输入电模拟压的数字值由下式得到;

多个触发器作为SOC序列的触发源;

-- S/W 软件触发 -- ePWM1-6触发 -- 通用GPIO触发

灵活的中断控制,允许在每个序列结束(EOS)或其他EOS上的中断请求;

顺序可以在“启动/停止”模式下操作,允许多个“时间顺序触发器”同步转换;

ePWM触发器可以在双序列模式下单独操作;

采样保持(S/H)采集时间窗口可以进行单独的预尺度控制;

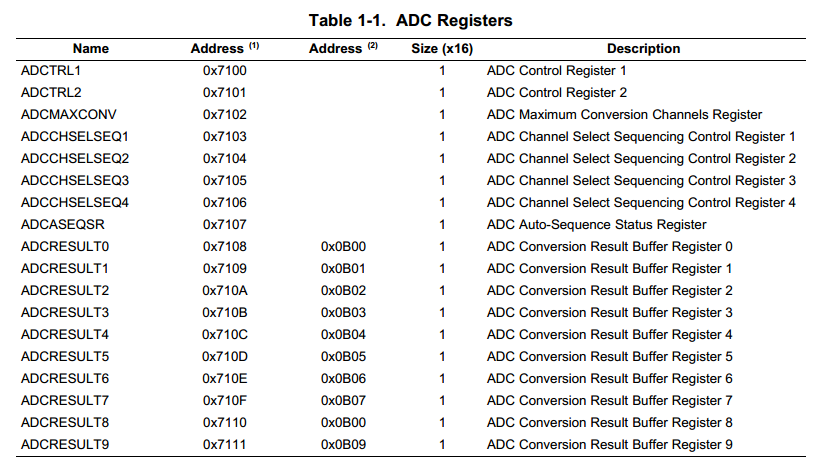

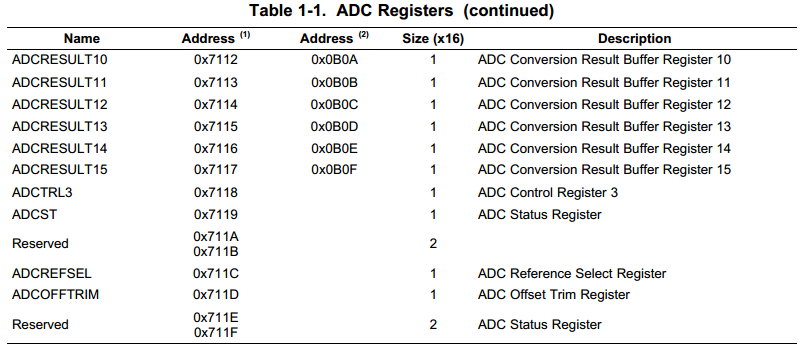

这一列中的寄存器是外围帧2寄存器。

ADC结果寄存器在器件中是双映射的。外围帧2(0x7108~0x7117)中的位置是两个等待状态,并左对齐。外围帧0(0x0B00~0x0B0F)中的位置为0等待状态并右对齐。在高速/连续转换使用ADC时,使用0等待状态未知以避免丢失ADC转换值。

2 自动转换定序器工作原理

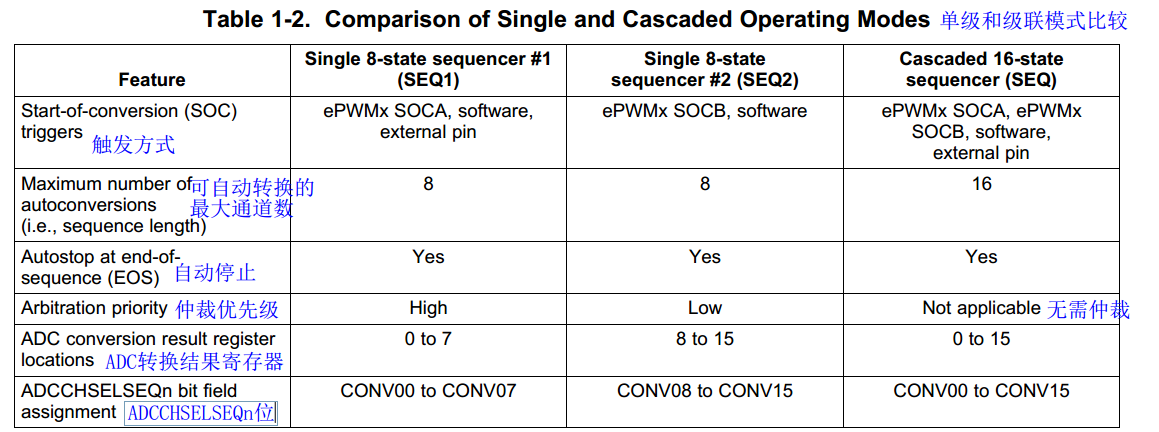

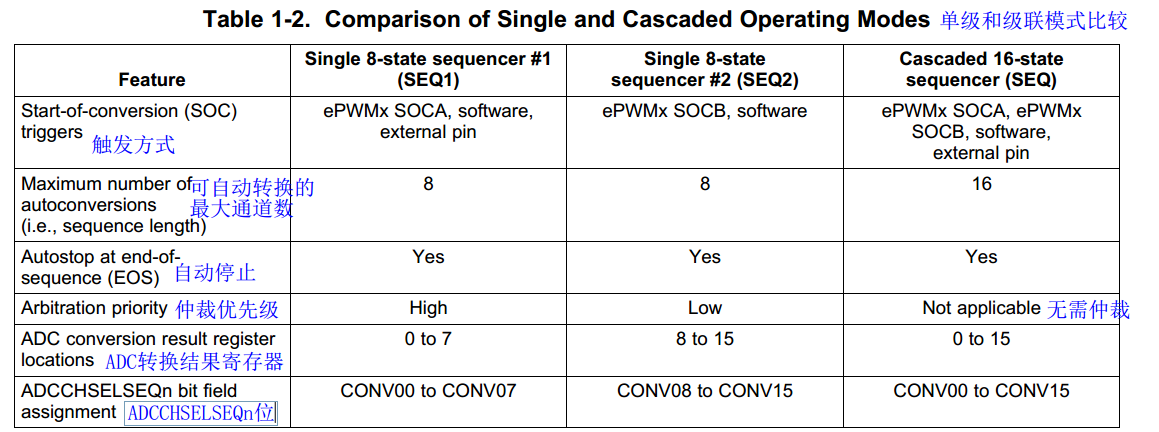

ADC定序器由两个独立的8状态定序器(SEQ1和SEQ2)组成,它们可以级联成一个16状态定序器(SEQ)。状态表示定序器自动转换的数量。单定序器模式(16状态)和双定序器(双8状态)模式如下图所示。在这两种情况下,ADC都具有自动排序转换的能力。这意味着每次ADC接收到一个开始转换请求时,它都可以自动执行多个转换。对于每次转换,可以通过MUX在16个输入通道选择任何一个可用的通道,所选通道的数值存储到相应的结果寄存器(ADCRESULTn)中。第一个存在(ADCRESULT0)中,第2个存在(ADCRESULT1)中。 可以对同一通道进行多次采样,允许执行“过采样”,这比传统的单采样转换结果提供了更高的分辨率。

Note:在顺序采样双定序器模式中,只要当前定序器的序列完成,任一定序器的待处理SOC请求就会被占用。例如:假设当来自SEQ1的SOC请求发生时,A/D转换器正在处理SEQ2的序列,A/D转换器将在完成SEQ2后立即启动SEQ1。如果来自SEQ1和SEQ2的SOC请求都处于挂起状态时,SEQ1的SOC的优先级更高,当SEQ1完成序列后,SEQ1的SOC请求立马被占用,SEQ2的SOC请求将继续等待。

单定序器模式

双定序器模式

Note:DSP只有一个ADC。该转换器在双定序器模式下由两个定序器共享。

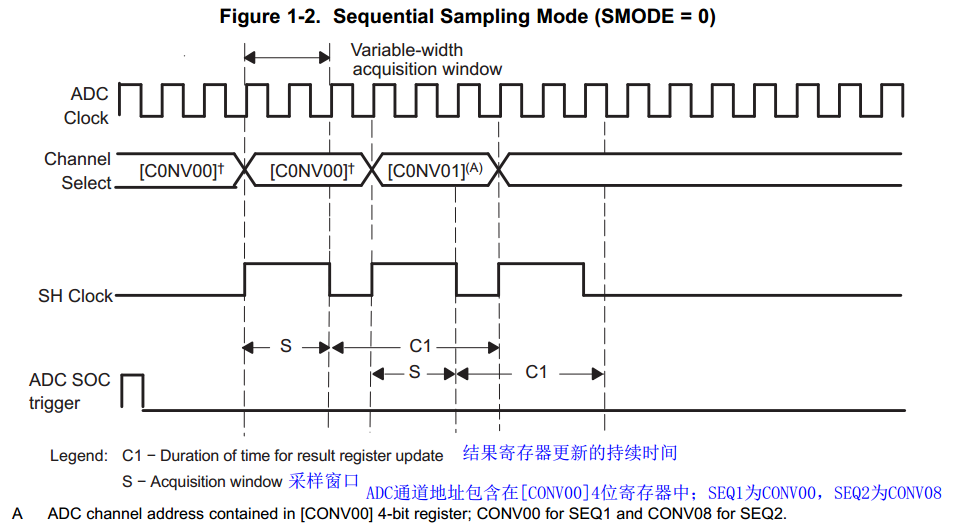

2.1 顺序采样模式

如下图为顺序采样模式时序图,配置ACQ_PS位设置为:0001b

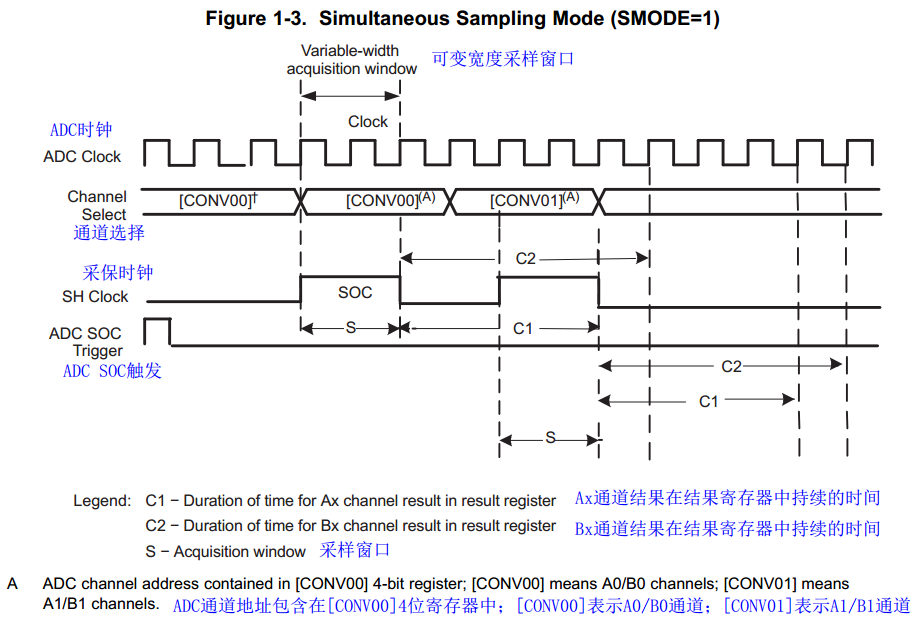

2.2 同步采样模式

如下图为同步采样模式时序图,配置ACQ_PS位设置为:0001b

顺序选择寄存器(ADCCHSELSEQn)中的CONVxx为是一个4位字段,用于指定16个通道中的任意一个进行转换。由于在级联模式下使用定序器是,一个序列中最多可以进行16次转换,因此可以使用16个这样的4位字段(CONV00-CONV15),并分布在4个16位寄存器(ADCCHSELSEQ1-ADCCHSELSEQ4)。CONVxx位可以使0~15的任意值。模拟通道可以以任何所需要的顺序选择,并且可以多次选择相同的通道。

/* Example 1-1.同步采样双定序器模式示例 */

/* 初始化 */

AdcRegs.ADCTRL3.bit.SMODE_SEL = 0x1; // Setup simultaneous sampling mode

AdcRegs.ADCMAXCONV.all = 0x0033; // 4 double conv's each sequencer (8 total)

AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0; // Setup conv from ADCINA0 & ADCINB0

AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x1; // Setup conv from ADCINA1 & ADCINB1

AdcRegs.ADCCHSELSEQ1.bit.CONV02 = 0x2; // Setup conv from ADCINA2 & ADCINB2

AdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0x3; // Setup conv from ADCINA3 & ADCINB3

AdcRegs.ADCCHSELSEQ3.bit.CONV08 = 0x4; // Setup conv from ADCINA4 & ADCINB4

AdcRegs.ADCCHSELSEQ3.bit.CONV09 = 0x5; // Setup conv from ADCINA5 & ADCINB5

AdcRegs.ADCCHSELSEQ3.bit.CONV10 = 0x6; // Setup conv from ADCINA6 & ADCINB6

AdcRegs.ADCCHSELSEQ3.bit.CONV11 = 0x7; // Setup conv from ADCINA7 & ADCINB7

/* 如果SEQ1和SEQ2都被执行,结果将会进入以下结果寄存器 */

ADCINA0 -> ADCRESULT0

ADCINB0 -> ADCRESULT1

ADCINA1 -> ADCRESULT2

ADCINB1 -> ADCRESULT3

ADCINA2 -> ADCRESULT4

ADCINB2 -> ADCRESULT5

ADCINA3 -> ADCRESULT6

ADCINB3 -> ADCRESULT7

ADCINA4 -> ADCRESULT8

ADCINB4 -> ADCRESULT9

ADCINA5 -> ADCRESULT10

ADCINB5 -> ADCRESULT11

ADCINA6 -> ADCRESULT12

ADCINB6 -> ADCRESULT13

ADCINA7 -> ADCRESULT14

ADCINB7 -> ADCRESULT15/* Example 1-2.同步采样级联定序器模式示例 */

/* 初始化 */

AdcRegs.ADCTRL3.bit.SMODE_SEL = 0x1; // Setup simultaneous sampling mode

AdcRegs.ADCTRL1.bit.SEQ_CASC = 0x1; // Setup cascaded sequencer mode

AdcRegs.ADCMAXCONV.all = 0x0007; // 8 double conv's (16 total)

AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0; // Setup conv from ADCINA0 & ADCINB0

AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x1; // Setup conv from ADCINA1 & ADCINB1

AdcRegs.ADCCHSELSEQ1.bit.CONV02 = 0x2; // Setup conv from ADCINA2 & ADCINB2

AdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0x3; // Setup conv from ADCINA3 & ADCINB3

AdcRegs.ADCCHSELSEQ2.bit.CONV04 = 0x4; // Setup conv from ADCINA4 & ADCINB4

AdcRegs.ADCCHSELSEQ2.bit.CONV05 = 0x5; // Setup conv from ADCINA5 & ADCINB5

AdcRegs.ADCCHSELSEQ2.bit.CONV06 = 0x6; // Setup conv from ADCINA6 & ADCINB6

AdcRegs.ADCCHSELSEQ2.bit.CONV07 = 0x7; // Setup conv from ADCINA7 & ADCINB7

/* 如果级联SEQ被执行,结果将进入一下结果寄存器 */

ADCINA0 -> ADCRESULT0

ADCINB0 -> ADCRESULT1

ADCINA1 -> ADCRESULT2

ADCINB1 -> ADCRESULT3

ADCINA2 -> ADCRESULT4

ADCINB2 -> ADCRESULT5

ADCINA3 -> ADCRESULT6

ADCINB3 -> ADCRESULT7

ADCINA4 -> ADCRESULT8

ADCINB4 -> ADCRESULT9

ADCINA5 -> ADCRESULT10

ADCINB5 -> ADCRESULT11

ADCINA6 -> ADCRESULT12

ADCINB6 -> ADCRESULT13

ADCINA7 -> ADCRESULT14

ADCINB7 -> ADCRESULT153 不间断自动排序模式

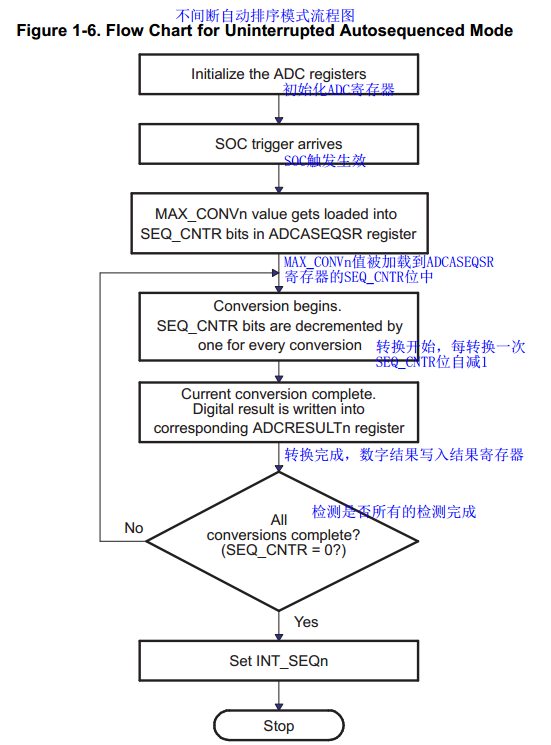

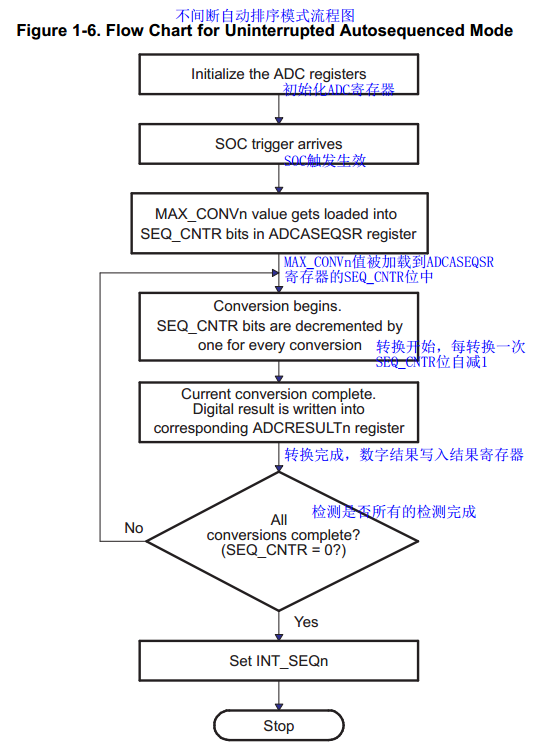

适用于8状态排序器(SEQ1或SEQ2)。在这种模式下,SEQ1/SEQ2可以在单个排序会话中自动排序8个任意通道的转换(当排序器级联到一起是为16)。如下图所示,每次转换的结果存储在早8个结果寄存器中的任意一个(SEQ1为ADCRESOULT0~ADCRESOULT7,SEQ2为ADCRESOULT8~ADCRESOULT15)。这些寄存器从最低地址填充到最高地址。

序列中的转换数量由MAX-CONVn(由ADCMAXCONV寄存器中的3位或4位字段控制),它在自动序列状态寄存器(ADCASEQSR)中自动加载到序列计数器状态为(SEQ_CNTR[3:0])在自动序列转换会话开始时。MAX_CONVn字段的值范围可以是0~7(当排序器级联在一起时是0~15)。当序列器从状态CONV00开始并依次(CONV01,CONV02,...)直到SEQ_CNTR达到零时,SEQ_CNTR位从加载值开始计数,在自动排序会话期间完成转换的数量等于(MAX_CONVn+1)。

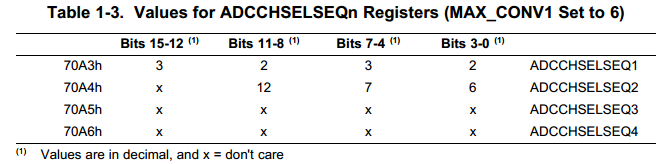

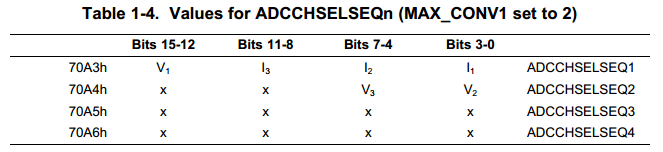

Example 1-3.转换在双排序模式使用SEQ1

假设需要从SEQ1进行7次转换(ADCINA2和ADCINA3各两次,然后ADCINA6、ADCINA7和ADCINA4必须作为自动排序会话的一部分进行转换),那么MAX_CONV1应该设置为6,ADCCHSELSEQn寄存器应设置为以下值。

一旦序列器接收到转换开始(SOC)触发,转换就开始了。SOC触发器也加在SEQ_CNTR位。在ADCCHSELSEQn寄存器中指定的那些通道按照预定的顺序进行转换。SEQ_CNTR位在每次转换后自动递减1.一旦SEQ_CNTR达到0,就会发生两件事,这取决于ADCTRL1寄存器中连续运行(CONT_RUN)的状态,如下图所示。

如果设置了CONT_RUN位,转换序列自动重新开始(即,SEQ_CNTR在MAX_CONV1中重新加载原始值,SEQ1状态被设置为CONV00),在这种情况下,为了避免覆盖数据,必须确保在下一个转换序列开始之前读取结果寄存器。如果ADC的仲裁逻辑出现竞争,结果寄存器不会损坏(ADC模块试图将结果写入结果寄存器,但同时其它程序又试图从结果寄存器中读取)。

如果没有设置CONT_RUN,那么排序器保持在最后的状态(在该示例中即为CONV06),并且SEQ_CNTR继续保持值为零,为了在下一个SOC上重复序列,必须在下一个SOC之前使用RST_SEQn位重置排序器。

如果每次SEQ_CNTR达到零(INT ENA_SEQn1和INT MOD_SEQn 0)时都设置中断标志,则可以(如果需要)在中断服务程序(ISR)中手动重置序列器(使用ADCTRL2寄存器中的RST_SEQn位)。这导致SEQn状态被重置为原始值(SEQ1为CONV00,SEQ2为CONV08)。此功能在启动和停止排序器是有用的,该示例同样的适用于SEQ2和级联的16状态排序器(SEQ)。差异参考下图。

3.1 排序器开始/停止工作

除了不间断自动排序模式外,任何排序器(SEQ1,SEQ2或SEQ)都可以在停止/启动模式下操作,该模式与多个SOC触发器同步,在时间上分开。这种模式类似于例1-3,但是一旦完成了它的第一个序列(即在ISR中没有重置序列器)就允许排序器被重新触发而不被重置到初始状态CONV00,因此当第一个转换序列结束时,排序器保持在当前转换状态。对于这种模式,ADCTRL1寄存器中的连续运行为(CONT_RUN)必须设置为0(禁用)。

Example 1-4.排序器开始/停止操作

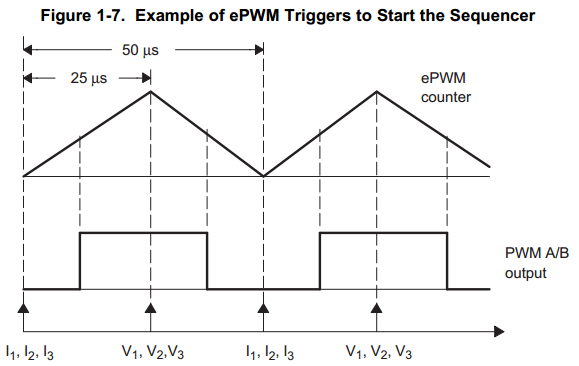

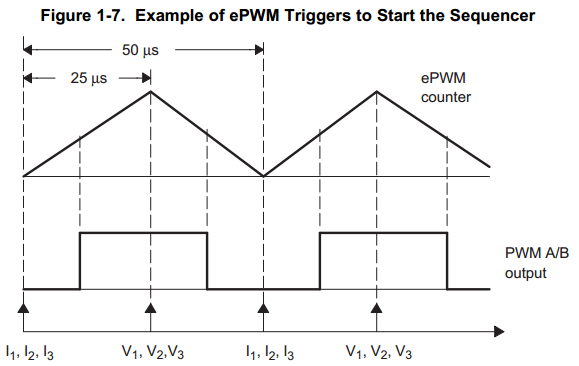

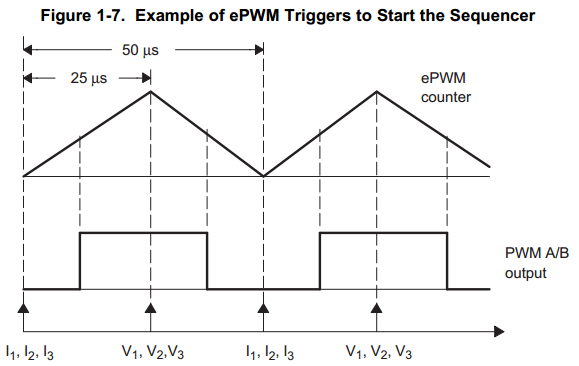

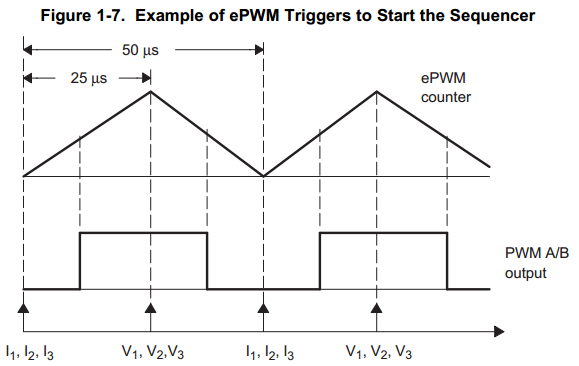

要求:同时启动三个自动转换,触发器1(下溢)触发(如 I_1、I_2、I_3)和触发器2触发(如 V_1、V_2、V_3),触发器1和2在时间上相隔25u秒,由ePWM提供,如下图所示,只使用了SEQ1。

Note:触发器1和2是可能来自ePWM触发、外部引脚触发或者软件触发。同一个触发源可以出现两次,以满足该例子的双触发需求。必须要注意避免多个触发器使得正在进行的转换序列丢失。

这里的MAX_CONV1配置为2,ADC输入通道选择时序控制器(ADCCHSELSEQn)的设置如下表所示:

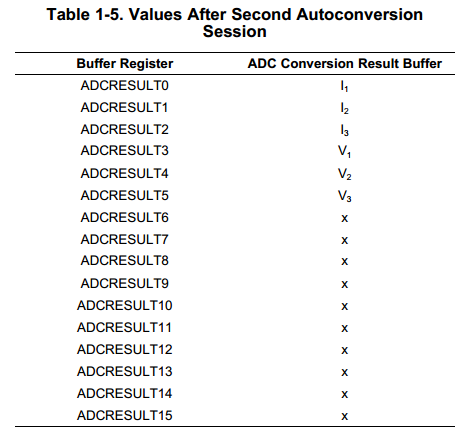

重置和初始化后,SEQ1等待触发器。对于第一个触发器,执行三个通道值的转换:CONV00(I_1)、CONV01(I_2)、CONV02(I_3)。然后,SEQ1在当前状态等待另外一个触发器。25us后,当第二个触发器到达,发生另外三个转换,通道选择之为CONV03(V_1)、CONV04(V_2 )、CONV05($V_3$)。对于这两种触发情况,MAX_CONV1的值都会自动加载到SEQ_CNTR中。如果在第二个触发点需要不同数量的转换,则必须(在第二个触发点之前的某个适当时间)通过软件更改MAX_CONV1的值否则将再次使用当前(最初加载的)值。这个可以通过中断在适当的时候改变MAX_CONV1的值来实现。在第二次自动转换会话结束时,ADC结果寄存器将具有下表的值。此时,SEQ1保持在当前状态“等待”另一个触发器。可以将SEQ1(软件)重置为CONV00状态,并重复相同的触发器1,2会话。

3.2 同步采样模式

ADC可以实现同时采样两个通道,要使用两个序列器(SEQ1、SEQ2)下的通道。两个输入必须保持相同的偏移,即ADCINA6和ADCINB6,(不包括ADCINA6和ADCINB7)。为了是的ADC进入同步采样模式,必须设置ADCTRL3寄存器的SMODE_SEL位。

3.3 顺序转换期间的中断操作

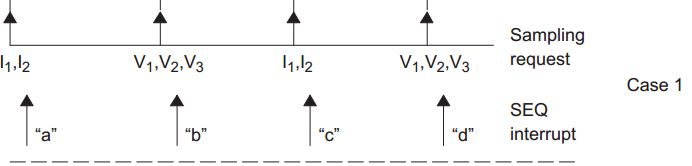

排序器可以在两种工作模式下产生中断,这些模式有ADCTRL2的Interrupt-Mode-Enable控制位决定。一个例1-4的变型可以用来展示中断模式1和模式2在不同操作条件下是如何使用的。

CASE1:第一个序列和第二个序列的样本数不相等

模式1中断操作(在每个EOS发生中断请求)

1、排序器初始化MAX_CONVn=1,用于转换 I_1、I_2;

2、在ISR“a”处,MAX_CONVn被更改为2(软件),用于转换 V_1、V_2、V_3;

3、在ISR"b"处执行以下事件

(a)MAX_CONVn再次更改为1,用于转换 I_1、I_2;

(b)从ADC结果寄存器读取 I_1、I_2和 V_1、V_2、V_3;

(C)排序器复位

4、重复2和3步骤,每次SEQ_CNTR达到零并且两个中断都被识别时都会设置中断标志。

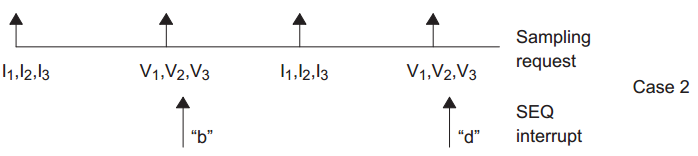

CASE2:第一个序列和第二个序列的样本数量相等

模式2中断操作(即在每个其他EOS发生中断请求)

1、排序器初始化为MAX_CONVn=2,用于转换 I_1、I_2、I_3和 V_1、V_2、V_3

2、在ISR"b"和“d”处执行以下事件:

(a)从ADC结果寄存器中读取 I_1、I_2、I_3和 V_1、V_2、V_3

(b)排序器复位

3、重复步骤2

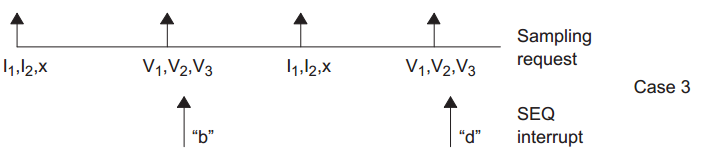

CASE3:第一个和第二个序列中的样本数量相等(带有假读取)

模式2中断操作(即在每个其他EOS发生中断请求)

1、对于 I_1、I_2、x(虚拟样本),排序器初始化为MAX_CONVn=2

2、在ISR"b"和“d”,发生以下事件

(1)从ADC结果寄存器中读取 I_1、I_2、x和 V_1、V_2、V_3

(2)排序器复位

3、重复步骤2。第三个样本(x)是一个虚拟样本,并不是真正需要的。然而为了最小ISR开销和CPU干预,利用模式2“每隔一次”中断请求特性。

4 ADC时钟预分频器

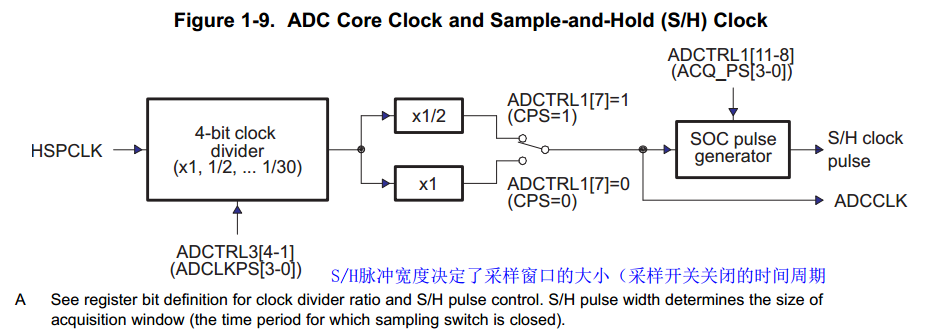

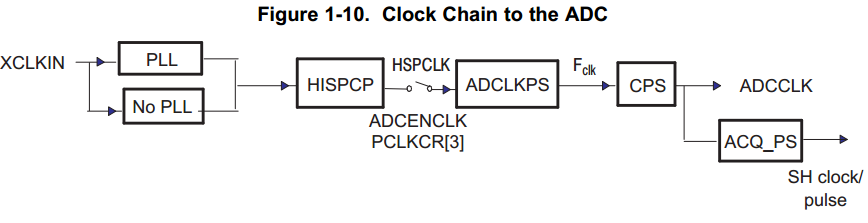

外围时钟HSPCLK被ADCTRL3寄存器的ADCCLKPS[3:0]位分频。通过ADCTRL1寄存器的CPS位提供一个额外的2分频。此外ADC可以通过扩大采样/采样周期来适应源阻抗变化,这是由ADCTRL1寄存器中的ACQ_PS[3:0]位控制。这些位不影响S/H的转换部分和转换过程,但通过延长转换脉冲的起始时间,延长采样部分所需的时间长度。如下图所示:

4.1 ADC模块时钟和采样频率

5 低功耗模式

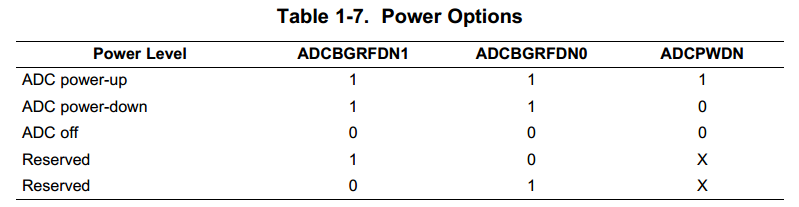

ADC支持3个独立的电源,每个电源都由ADCTRL3寄存器的独立位控制。这三个位组合起来构成三个功率电平:ADC上电、ADC掉电、ADC关断。

6 上电顺序

ADC复位为ADC关断状态。当给ADC上电是,使用一下顺序:

1、如果需要外部引用,使用ADCREFSEL寄存器中的15-14位启用该模式,带隙上电前必须启用该模式;

2、通过在ADCTRL3寄存器中设置7-5位(ADCBGRFDN[1:0],ADCPWDN),将参考电路、带隙电路和模拟电路一起上电。

3、在执行第一次转换前需要5ms的延迟。

当关闭ADC电源时,所有3bit都可以同时清除。ADC的功率电平必须通过软件进行控制,并且与器件功率模式的状态无关。若需要通过仅清除ADCPWDN位来关闭ADC的电源,同时保留带隙和参考电源。当ADC重新上电时,在执行任何转换之前设置此位后需要20us的延迟

评论区